Що таке ПЛІС: поняття, визначення, правила програмування та основи для початківців

ПЛІС (FPGA) розшифровується як "Field Programmable Gate Array" і являє собою величезний масив вентилів, які можуть бути запрограмовані і перебудовані в будь-який час і в будь-якому місці. Багато користувачів до цих пір не розуміють, що таке ПЛІС. «Величезний набір воріт» — спрощений опис моделі. Деякі FPGA мають вбудовані жорсткі блоки: контролери пам'яті, високошвидкісні комунікаційні інтерфейси і кінцеві точки PCIe. Всередині FPGA багато вентилів, які можна вільно з'єднати разом. Принцип роботи більш або менш схожий на підключення окремих мікросхем логічних елементів. FPGA випускаються провідними компаніями світу Xilinx, Altera, і Microsemi.

Altera була створена в 1983 році, а вже в 1984 році випустила перший в галузі який можна перепрограмувати логічний пристрій — EP300 з кварцовим вікном в упаковці, що дозволило використовувати ультрафіолетову лампу на матриці для видалення EPROM мітки. Щоб подолати труднощі вартості і швидкості, була розроблена програмована логіка масиву, в яку входив лише один програмований «І», що вводиться в фіксовані «АБО» ворота. PAL і PLA разом з іншими варіантами групуються як прості програмовані логічні пристрої SPLD. Такі ПЛІС, що інтегровані в один чіп з наданими міжз'єднаннями для програмного з'єднання блоків, використовувалися для задоволення зростаючих технологічних вимог. Вони названі комплексними PLD і розроблені Altera.

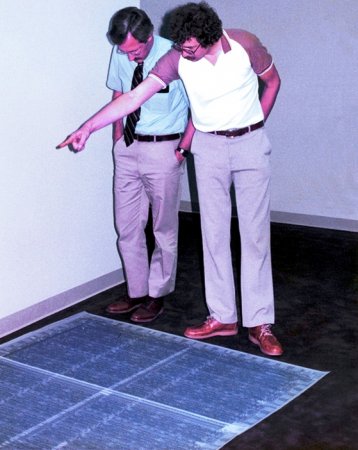

Транзистори — інший клас електронних пристроїв на основі програмованих масок масивів затворів. Вони складаються з транзисторних масивів, які можуть бути підключені за допомогою користувальницьких проводів. Вони поступилися місцем логічним блокам, і тепер користувач може настроювати на місці, а не у виробничій лабораторії. Ідея розробки першою комерційно життєздатною ПЛІС належить співзасновникам Xilinx Россу Фрімену і Бернарду Вондершмитту. XC2064 був винайдений в 1985 році і складався з 64 настроюваних логічних блоків з 3-ма довідковими таблицями. Він дає сучасне розуміння, що таке ПЛІС. Це було наприкінці 1980 року, коли запропонований Стівом Кассельман експеримент по створенню комп'ютера з 6000000 перепрограмованих воріт знайшов спонсорів у відділі надводних бойових дій ВМС США, а потім отримав патент в 1992 році. До кінця 1990 року з'явилася велика конкуренція у виробництві ПЛІС, тоді частка ринку Xilinx почала знижуватися. Такі гравці, як Actel, Altera, Lattice, QuickLogic, Cypress, Lucent і SiliconBlue, зайняли свою нішу на світовому ринку FPGA поряд з Xilinx. У 1997 році Адріану Томпсону вдалося об'єднати програмування ПЛИСов і технологію генетичного алгоритму з FPGA, почавши нову епоху Evolvable.

Сьогодні ПЛІС стали досить доступними, у зв'язку з чим продовжують завойовувати популярність на споживчих ринках. Вони складаються з набору логічних комірок, що називаються таблицями пошуку LUT, оточених межкомпонентной мережею, що забезпечує гнучку систему, яка може реалізувати практично будь-який цифровий алгоритм.

Verilog — це мова опису апаратних засобів HDL, який можна використовувати для цифрових схем в текстовому вигляді. Вивчення Verilog не так складно, якщо у користувача є досвід програмування. VHDL є ще одним популярним HDL, широко використовуваним в галузі. Verilog та VHDL мають більш або менш однакове визнання на ринку, але користувачі зазвичай вибирають Verilog, оскільки він простий у вивченні і має синтаксичне схожість з мовою Сі.

Проектування FPGA передбачає в основному той же підхід, що і будь-яка система VLSI, основними етапами якої є проектування, моделювання поведінка, синтез, моделювання після синтезу, трансляція, відображення і маршрутизація, а також подальший аналіз, такий як моделювання синхронізації та статичний аналіз синхронізації. На комп'ютері дизайн виглядає впорядкованим і покладеним плиткою, однак фактично є недосконале розміщення та маршрутизація, що призводить до зниження продуктивності. Щоб підвищити продуктивність FPGA, завжди можна використовувати більше транзисторів. Службова площа висока. Установка більшої кількості транзисторів означає, що можливі масштабні конструкції. Витік є серйозною проблемою для ПЛІС і в той же час являє інтерес. Використання асинхронної архітектури FPGA показує кращі результати в поєднанні з технологією конвеєрної обробки, яка зменшує глобальні входи і покращує пропускну здатність.

Історія розвитку FPGA

Індустрія ПЛІС зросла з програмованою постійної пам'яті PROM і логічних пристроїв PLD. У 1970 р. Philips винайшов програмовану в польових умовах матрицю. У конструкції такої ПЛІС, що складалася з двох планів, досягалася специфічна реалізація логічних схем: функціональна дротова "І" або "АБО". Це давало їй можливість реалізації функції у вигляді Sum of Products.Altera була створена в 1983 році, а вже в 1984 році випустила перший в галузі який можна перепрограмувати логічний пристрій — EP300 з кварцовим вікном в упаковці, що дозволило використовувати ультрафіолетову лампу на матриці для видалення EPROM мітки. Щоб подолати труднощі вартості і швидкості, була розроблена програмована логіка масиву, в яку входив лише один програмований «І», що вводиться в фіксовані «АБО» ворота. PAL і PLA разом з іншими варіантами групуються як прості програмовані логічні пристрої SPLD. Такі ПЛІС, що інтегровані в один чіп з наданими міжз'єднаннями для програмного з'єднання блоків, використовувалися для задоволення зростаючих технологічних вимог. Вони названі комплексними PLD і розроблені Altera.

Транзистори — інший клас електронних пристроїв на основі програмованих масок масивів затворів. Вони складаються з транзисторних масивів, які можуть бути підключені за допомогою користувальницьких проводів. Вони поступилися місцем логічним блокам, і тепер користувач може настроювати на місці, а не у виробничій лабораторії. Ідея розробки першою комерційно життєздатною ПЛІС належить співзасновникам Xilinx Россу Фрімену і Бернарду Вондершмитту. XC2064 був винайдений в 1985 році і складався з 64 настроюваних логічних блоків з 3-ма довідковими таблицями. Він дає сучасне розуміння, що таке ПЛІС. Це було наприкінці 1980 року, коли запропонований Стівом Кассельман експеримент по створенню комп'ютера з 6000000 перепрограмованих воріт знайшов спонсорів у відділі надводних бойових дій ВМС США, а потім отримав патент в 1992 році. До кінця 1990 року з'явилася велика конкуренція у виробництві ПЛІС, тоді частка ринку Xilinx почала знижуватися. Такі гравці, як Actel, Altera, Lattice, QuickLogic, Cypress, Lucent і SiliconBlue, зайняли свою нішу на світовому ринку FPGA поряд з Xilinx. У 1997 році Адріану Томпсону вдалося об'єднати програмування ПЛИСов і технологію генетичного алгоритму з FPGA, почавши нову епоху Evolvable.

Сьогодні ПЛІС стали досить доступними, у зв'язку з чим продовжують завойовувати популярність на споживчих ринках. Вони складаються з набору логічних комірок, що називаються таблицями пошуку LUT, оточених межкомпонентной мережею, що забезпечує гнучку систему, яка може реалізувати практично будь-який цифровий алгоритм.

Принципи програмування

Програмування ПЛІС для початківців — це процес вивчення, планування, проектування та реалізації рішення на FPGA. Кількість і тип планування варіюються від програми до програми. Створення документа з вимогами та створення документа з дизайном, з поясненням, як буде реалізовано пропоноване рішення, може бути дуже корисним для вирішення потенційних проблем. Час, витрачений на створення якісного проектного документа, заощадить його в майбутньому на рефакторинге, налагодження і виправлення помилок. Реалізація рішення з допомогою програмування ПЛІС включає в себе створення проекту з використанням одного з методів впровадження проекту. Серед них схеми або код HDL, наприклад, Verilog або VHDL. FPGA можуть запрограмувати вихідний файл на фізичний пристрій FPGA з використанням інструментів програмування ПЛІС Altera. Введення дизайну з застосуванням схем більше не використовується в промисловості. Синтез і програмування майже повністю подбали про інструменти вендора, таких як інструменти конфігурації ISE і Vivado і Numato Lab.Рівень передачі регістра RTL

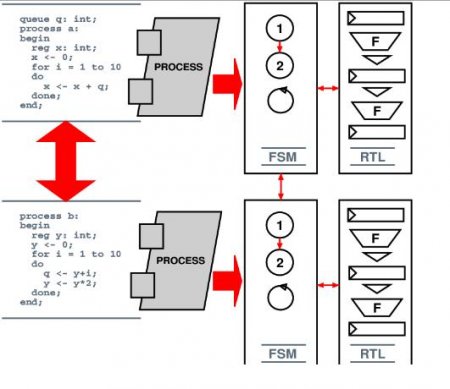

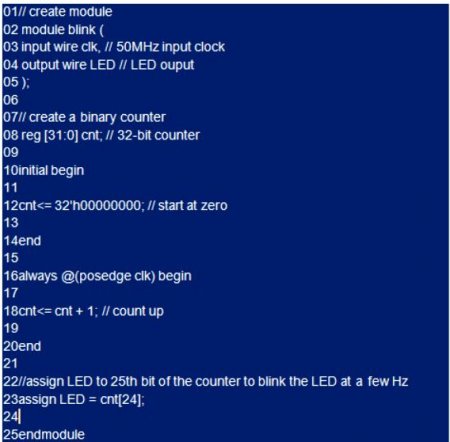

RTL позначає рівень передачі регістра. Розробник також може зіткнутися з термінами Register Transfer Logic або Register Transfer Language, всі вони означають одне і те ж в контексті проектування обладнання. RTL — це абстракція більш високого рівня для цифрового апаратного дизайну, яка знаходиться десь між строго поведінковим моделюванням на одному кінці і чисто структурним на рівні шлюзу — на іншому. Моделювання гейтів означає опис апаратних засобів з використанням базових вентилів, що є досить виснажливим. RTL можна розглядати як аналог терміна «псевдокод», використовуваного в основи програмування ПЛІС. Можна описати апаратний дизайн як послідовність кроків або потоку даних від одного набору регістрів до наступного в кожному тактовому циклі. RTL також називають дизайном «потоку даних». Як тільки проект RTL готовий, його легше перетворити в реальний код HDL, використовуючи такі мови, як Verilog, VHDL, SystemVerilog або будь-який інший мову опису обладнання. ПЛІС — це набагато більше, ніж просто безліч воріт. Хоча можна будувати логічні схеми будь-якої складності, організовуючи і з'єднуючи логічні елементи. Це спосіб виразити логіку в простому форматі, який в кінцевому підсумку можна перетворити в масив елементів. Два популярних методу зробити це: введення схеми і мови опису обладнання HDL. До того, як він став широко використовуваним, інженери проектували все з допомогою схем. Вони були дуже простими для невеликих проектів, але болісно некерованими — для великих. Варто тільки уявити собі, як інженери Intel малюють схеми для Pentium, у якого мільйони шлюзів! Це неприйнятно складно.Verilog — це мова опису апаратних засобів HDL, який можна використовувати для цифрових схем в текстовому вигляді. Вивчення Verilog не так складно, якщо у користувача є досвід програмування. VHDL є ще одним популярним HDL, широко використовуваним в галузі. Verilog та VHDL мають більш або менш однакове визнання на ринку, але користувачі зазвичай вибирають Verilog, оскільки він простий у вивченні і має синтаксичне схожість з мовою Сі.

Технології програмування

ПЛІС можна вважати будівельними блоками, які дозволяють здійснити потрібну настройку устаткування. Це особлива форма PLD з більш високою щільністю і розширеними можливостями функціоналу за більш короткий проміжок часу з використанням CAD. ПЛІС доступні в різних варіантах на основі використовуваної технології програмування. Вони можуть бути запрограмовані з використанням: Antifuse Technology. Програмування на основі технології Flash пристрої від Actel. FPGA може бути перепрограмований кілька тисяч разів, що займає кілька хвилин у самому поле для перепрограмування і має енергонезалежну пам'ять. ПЛІС на основі технології SRAM, яка пропонує необмежену перепрограмування і дуже швидку реконфігурацію або часткову реконфігурацію під час самої роботи з невеликою кількістю додаткових схем. Більшість таких компаній, як Altera, Actel, Atmel і Xilinx, виробляють ці пристрої.Конфігуровані логічні блоки

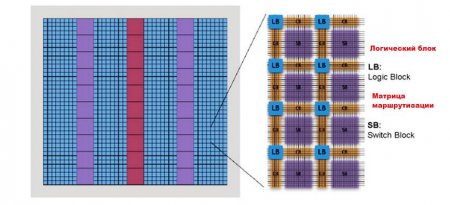

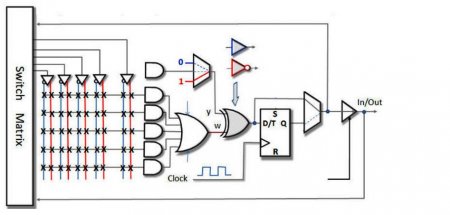

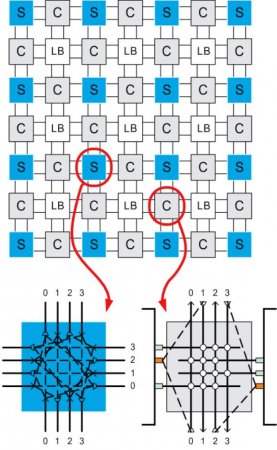

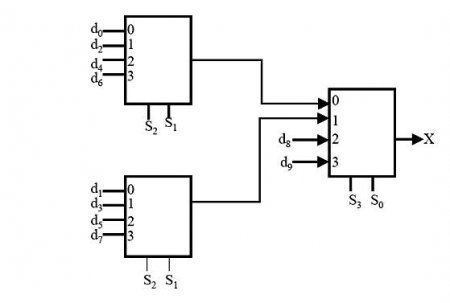

Незалежно від різних виробників і кілька різних архітектур і наборів функцій, більшість FPGA має загальний підхід. Основними компонентними блоками будь FPGA є гнучкий програмований «логічний блок» (CLB), оточений програмованими «блоками введення /виведення» з ієрархією маршрутизації каналів, що з'єднують різні блоки на платі. Крім того, вони можуть складатися з DLL-бібліотек для розподілу і управління годинами і пам'яті RAM вибраного блоку з основним будівельним блоком логічної осередком. Остання складається з генератора вхідних функцій, логіки перенесення і зберігання елементів. Генератори реалізуються у вигляді довідкових таблиць і залежать від введення. Наприклад, Xilinx Spartan II має 4 вхідних LUT із забезпеченням кожного 16X1 бітним синхронним ОЗП з використанням мультиплексорів як регістрів зсуву для захоплення даних в пакетному режимі. Елементи зберігання є чутливими до країв тригерів або до рівня засувок. Фрагмент програмування ПЛИСов: Арифметична логіка включає в себе вентиль XOR для роботи з повним суматором і виділенням логічних ліній перенесення. Блок вводу /виводу і матриця маршрутизації. Цей блок має входи і виходи, що підтримують широкий спектр стандартів і інтерфейсів сигналізації. Базовий блок вводу /виводу показаний нижче. Буфер під вхідних і вихідних шляхах надсилають сигнали у внутрішню логіку і підсумкові майданчика безпосередньо або через тригер. Вони налаштовуються на відповідність різним підтримуваних стандартів сигналізації, які можуть бути визначені користувачем і встановлені ззовні.Матриця маршрутизації

На будь складальної лінії повільний сегмент визначає загальну продуктивність. Алгоритми маршрутизації використовуються для розробки найбільш ефективних шляхів забезпечення оптимальної продуктивності. Маршрутизація здійснюється на різних рівнях, таких, як локальний, маршрутизація загального призначення між різними CLB, маршрутизація вводу-виводу між блоками і CLB, виділена маршрутизація для певних сигнальних класів з метою максимізації продуктивності і Global Routing для розподілу тактових та інших сигналів з дуже великим розгалуженням. Сімейства FPGA також мають великі блокові структури RAM для доповнення розподілених LUT RAM, розмір яких варіюється для різних пристроїв FPGA.Проектування FPGA передбачає в основному той же підхід, що і будь-яка система VLSI, основними етапами якої є проектування, моделювання поведінка, синтез, моделювання після синтезу, трансляція, відображення і маршрутизація, а також подальший аналіз, такий як моделювання синхронізації та статичний аналіз синхронізації. На комп'ютері дизайн виглядає впорядкованим і покладеним плиткою, однак фактично є недосконале розміщення та маршрутизація, що призводить до зниження продуктивності. Щоб підвищити продуктивність FPGA, завжди можна використовувати більше транзисторів. Службова площа висока. Установка більшої кількості транзисторів означає, що можливі масштабні конструкції. Витік є серйозною проблемою для ПЛІС і в той же час являє інтерес. Використання асинхронної архітектури FPGA показує кращі результати в поєднанні з технологією конвеєрної обробки, яка зменшує глобальні входи і покращує пропускну здатність.

Якість і проблеми воріт

Безпека системи завжди була головною проблемою, так як код повинен розкриватися кожен раз, коли завантажувався в ПЛІС. Така гнучкість робить FPGA потенційною загрозою шкідливих модифікацій при виготовленні, тому шифруванні бітових потоків вчасно прийшов йому на допомогу. Часто недосвідчені дизайнери і користувачі стикаються з дилемою, наскільки потужна ПЛІС підходить для їх розробок. Виробники часто вказують метрики, наприклад, «кількість воріт». Наприклад, програмування ПЛІС Xilinx використовує 3 метрики для вимірювання об'єму FPGA, максимальних логічних елементів, максимальних бітів пам'яті і типового діапазону шлюзів. Поки вони є узгодженими, міграція між моделями дещо спрощується, але вона рідко пропонує точне порівняння у різних постачальників через різноманітність в архітектурі і з-за відмінностей в продуктивності. Найкращим показником є порівняння типу і кількості наданих логічних ресурсів. На додаток до цього, розробник повинен повністю усвідомити, що саме потрібно від пристрою, оскільки виробники можуть похвалитися можливостями, які будуть мати найменше значення для роботи. Наприклад, Stratix II EP2S180 від Altera має близько 186576 LUT з 4 входами, а Xilinx Virtex-4 XC4VLX200 містить відповідно 178176. Однак, якщо для проектування потрібна лише 177 тис. LUT, це буде досить. Якщо ОЗП - це бажана метрика для дизайнера, то ні 6 Мбіт Xilinx XC4VLX200 ні 9 Мбіт Altera EP2S180 не будуть кращі, порівняно з менш рекламованої, більш старою моделлю XC4VFX140 з 99 Мбіт.Мови програмування і ПО

Програмування ПЛІС Altera для початківців стартує з вибору мови. Опція C, C ++ або System C дозволяє використовувати можливості найбільших пристроїв і, в той же час, досягнення подібності реалістичної графіки розробки. Можливість використання на базі C для проектування FPGA забезпечується HLS (синтез високого рівня), який вже багато років знаходиться на межі прориву з таким інструментом, як Handle-C. останнім часом це стало реальністю завдяки тому, що великі постачальники Altera і Xilinx пропонують HLS у своїх наборах інструментів Spectra-Q і Vivado HLx відповідно. Доступний ряд інших реалізацій програмування ПЛІС Altera для початківців на основі C, таких як OpenCL, який призначений для розробників програмного забезпечення, які бажають підвищення продуктивності з допомогою FPGA без глибокого розуміння дизайну FPGA. Як і у випадку з HDL, HLS має обмеження при використанні підходів програмування ПЛІС на C, як і з традиційними HDL, розробникам доводиться працювати з підмножиною мови. Наприклад, важко синтезувати і реалізувати системні виклики, так як потрібно переконатися, що всі обмежена і має фіксований розмір. У HLS приємно те, що можна розробляти свої алгоритми з плаваючою комою і є інструмент HLS перетворення плаваючою комою в фіксовану. Програмувати ПЛІС з Xilinx зовсім не складно. Отримати його можна, купуючи продукти Xilinx, безкоштовно або за ціною, орієнтованої на конкретні моделі. Можна отримати доступ до відео на профільному сайті, який наочно показує процедуру використання. З усіх компаній, які можна вибрати при пошуку програмованих вентильних масивів, Xilinx безумовно кращий з усіх. Вони є творцями цього продукту, і протягом багатьох років вносили у нього поліпшення. Фірмове ПЗ стало більше потужним, ніж коли-небудь раніше.Етапи проектування

Навчання програмування ПЛІС можна проводити онлайн, оскільки платформа добре представлена в інтернеті. При настроювання ПЛІС першим кроком є проектування схеми, для якої необхідне знання цифрової електроніки. На відміну від програмування, набагато складніше почати нарізку коду, якщо архітектура програми не ясна. Як тільки стане ясно, що потрібно реалізувати, приступають до опису схеми, використовуючи один з мов: Verilog або VHDL. Факт, який свідчить про зміну парадигми, полягає в тому, що вони не називаються мовами програмування ПЛІС, а є мовами опису. Із-за складності тестування цифрових схем зазвичай на цьому етапі використовуються банки тестів, що моделюють поведінку обладнання. Цей тип інструментів дозволяє бачити стан сигналу в будь-який момент і перевіряти, чи є переходи з бажаними результатами. Третій етап відомий як синтез схеми є одним з ключових. Він вибирає використовувані елементи та їх взаємозв'язок у відповідності з файлами опису. Для цього етапу потрібні інструменти, які в більшості ситуацій спрощують і автоматизують завдання.Апаратні засоби та налагодження

Intel Quartus Prime Software Suite Lite Edition — програмне забезпечення для проектування ПЛІС. Воно ідеально підходить для початківців, так як його можна завантажити безкоштовно, а файл ліцензії не потрібно. Можна завантажити програмне забезпечення на сайті виробника. Розмір (кілька гігабайт), їх завантаження і установка може зайняти багато часу. Щоб мінімізувати час і необхідний дисковий простір, рекомендується завантажувати тільки ті елементи, які необхідні для користувальницьких задач. При запиті, файли для завантаження, знімають прапорець «Select All» і вибирають тільки Quartus Prime і підтримку Cyclone V пристрою. Алгоритм створення проекту: Відкривають Майстер нового проекту. Вибирають Next > Каталог > > Ім'я об'єкт верхнього рівня. Вибирають каталог для розміщення проекту, наприклад, «Blink» і поміщають його в папку intelFPGA_lite, але можна розмістити де завгодно і натискають «Далі». Коли буде запропоновано створити каталог, вибирають «Так». Вибирають «Порожній проект» і натисніть «Далі». Додають файли і «Далі». Налаштовують сімейства, пристрою і плати, вибираючи таке: сім'я - Циклон V, пристрій - Циклон V SE, база, назва пристрою: 5CSEBA6U2317. Щоб вибрати конкретний пристрій, потрібно натискати стрілки вгору /вниз, щоб побачити список підтримуваних пристроїв, поки не з'явиться 5CSEBA6U2317. Користувачеві може знадобитися розширити поле «Ім'я», щоб побачити повне ім'я пристрою, натиснути «Далі». При налаштуванні інструмент EDA, використовують стандартні інструменти, тому ніяких змін не буде, натискають «Далі» і «Готово». З'явиться екран резюме. Створюють файл HDL з впровадженням Verilog як HDL. Переходять на вкладку File (головне вікно) і вибирають New. Вибирають Verilog HDL File і натискають кнопку ОК. Вибирають «Файл»> «Зберегти як». Вибирають ім'я файлу. Це ім'я файлу верхнього рівня, і воно має збігатися з ім'ям проекту. Натисніть «Зберегти». Створюють модуль Verilog. Копіюють і вставляють нижче розміщений код Verilog у вікно blink.v, а потім зберігають файл коду. Натискають правою кнопкою миші «Аналіз і синтез», а потім натискають «Пуск», щоб виконати перевірку синтаксису і синтезу коду Verilog. Якщо процес завершується успішно, поряд з аналізом і синтезом відображається зелена галочка. Якщо помилка, перевіряють синтаксис і переконуються, що він точно відповідає блоку коду, вказаному вище. Всі досвідчені програмісти знають, що складні програми, навіть підпрограми, не працюють правильно з першого разу. Здатності до абстракції у людини, засновані на досвіді, дозволяють йому знаходити рішення, не турбуючись про найдрібніших деталях. Але сувора правда полягає в тому, що фізична система, в яку вбудовуються програми, вимагає, щоб кожна дрібниця була врахована, перш ніж все запрацює. З поліпшенням програмних інструментів для розробки ПЛІС в основному від традиційних постачальників, а також незалежних постачальників інструментів: Synplicity, FPGA — стає день від дня все більш популярною. Тепер ПЛІС почали включати спеціалізоване апаратне забезпечення необхідних клієнту функцій, знижуючи витрати виробників. Таким чином, в майбутньому може з'явитися конкуренція між жорсткими і дешевими системами з гнучкими ядрами. Очікується, що в найближчому майбутньому витрати будуть знижуватися ще більше, оскільки популярність FPGA зросте в рази. Виробники почали експериментувати з таким поняттям, як вбудовування ПЛІС в інтегральні мікросхеми для створення гібридного пристрою. Основна увага як і раніше приділяється маршрутизації межз'єднань, а в архітектурах CLB спостерігаються менші зміни. Оскільки ПЛІС продовжують включати процесори, нове покоління вимагає не тільки знань апаратного забезпечення цифрового дизайну, але і досвіду розробників в процесі одноразового програмування ПЛІС. В цілому, очікується, що FPGA відніме частку ринку в пристроях ASIC і стане домінуючою технологією, що охоплює безліч додатків з різних областей.Цікаво по темі

CRM-системи: рейтинг, топ кращих, призначення, розробка, принцип роботи та застосування

Автоматизація процесу бізнесу - це невід'ємна його частина. Складський і бухгалтерський облік давно вже автоматизовано в провідних компаніях. Але це

Системи програмування: приклади, опис, особливості

Системи програмування забезпечують платформу для розробки прикладного програмного забезпечення і безпосередньо взаємодіють з комп'ютерним

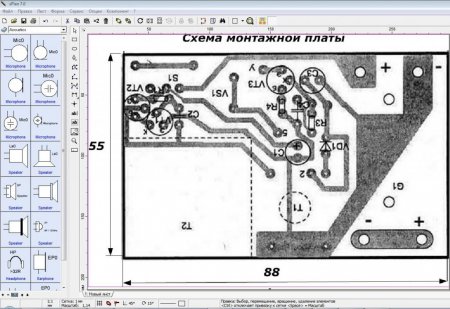

Популярні програми для малювання схем

Все частіше ми використовуємо для роботи комп'ютер і його віртуальні інструменти. Навіть креслити тепер на папері схеми і проекти не всім і не завжди

Зміст і використання JavaScript void

Відсутність значення і значення undefined - раритет найдавніших часів інформаційних технологій, але навіть в сучасному світі у них є місце і

Що таке програмування? Мови програмування. Комп'ютерне програмування

В період появи перших комп'ютерних систем гостро постало питання того, як «навчити» машину сприймати ...